# LogiCore™ PCI Master and Slave Interface User's Guide

November 1, 1996 (Version 1.1)

LC-DI-PCIM-C and LC-DI-PCIS-C

| Table of Contents                                |

|--------------------------------------------------|

| 1. Introduction 1                                |

| 2. Getting Started 3                             |

| 3. Design Methodology3                           |

| 4. LogiCore PCI Interface Operation 4            |

| 5. Signal Descriptions 5                         |

| 6. Building a Complete PCI Design17              |

| 7. Customizing the LogiCore PCI Interface 18     |

| 8. General Design Guidelines25                   |

| 9. Target Data Transfers and Control 28          |

| 10. Initiator Data Transfers and Control 29      |

| 11. Data Flow Control Signals30                  |

| 12. Target-Initiated Terminations30              |

| 13. Automatic Wait-State Insertion31             |

| 14. Handling Burst Transfers 32                  |

| 15. Tips for Building an Initiator Controller 35 |

| 16. Controlling Initiator Transactions 36        |

| 17. Design Validation Process                    |

| 18. Compliance Process 43                        |

| 19. Appendix A: Pinout, Configuration 44         |

| 20. Appendix B: Resources 47                     |

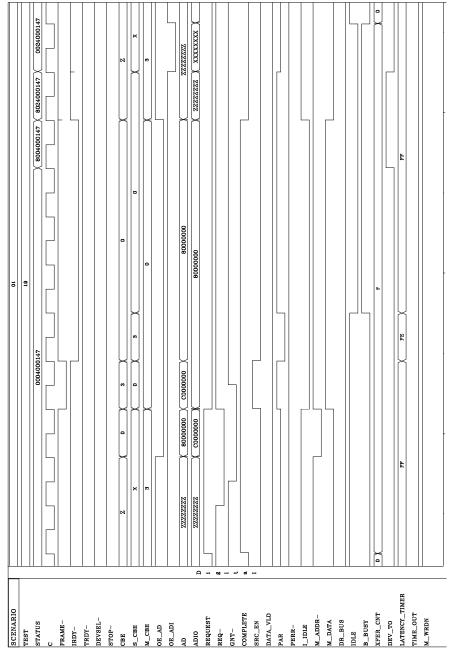

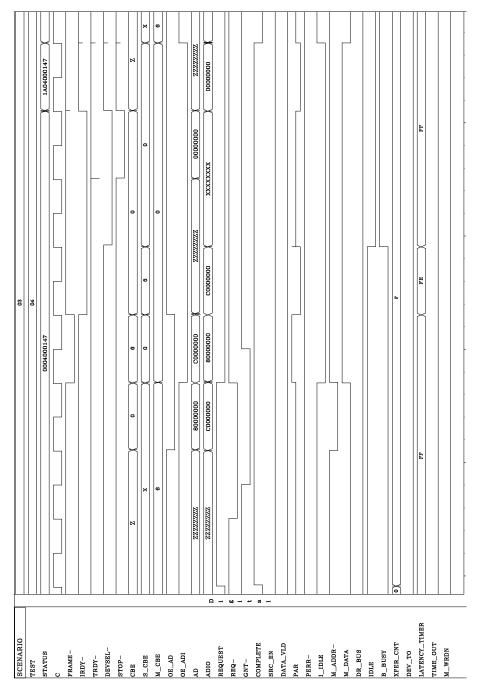

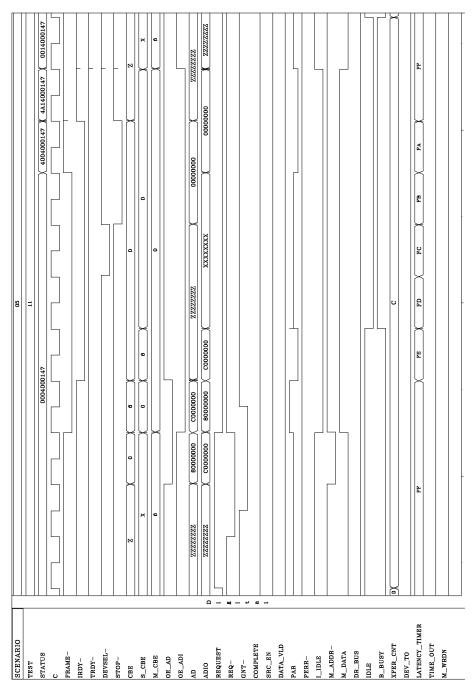

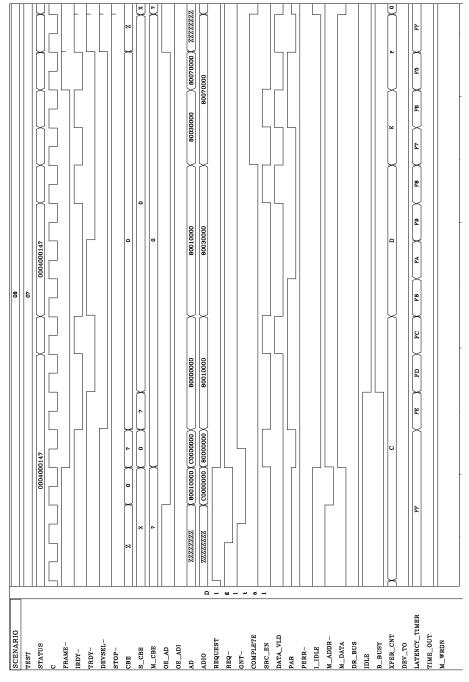

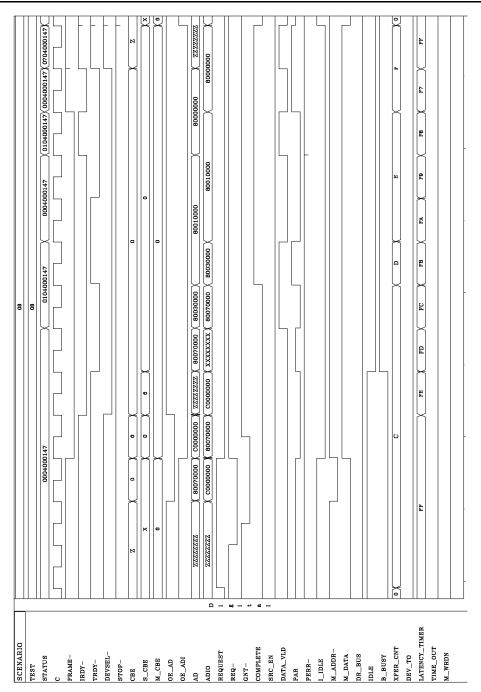

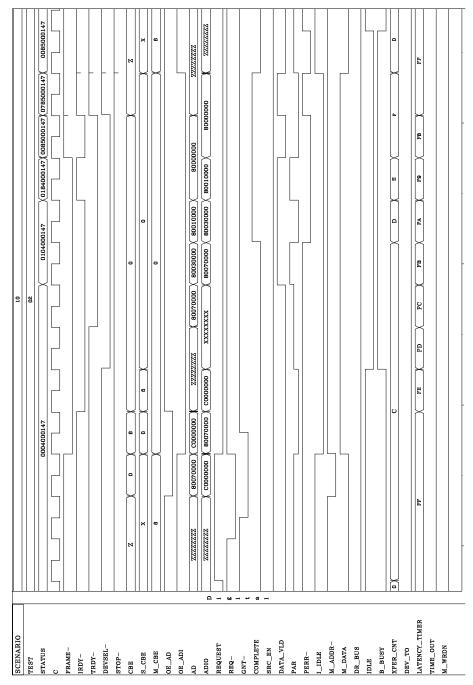

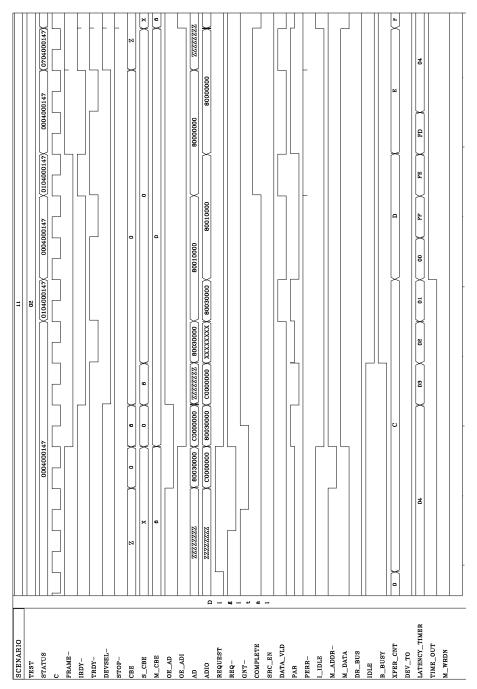

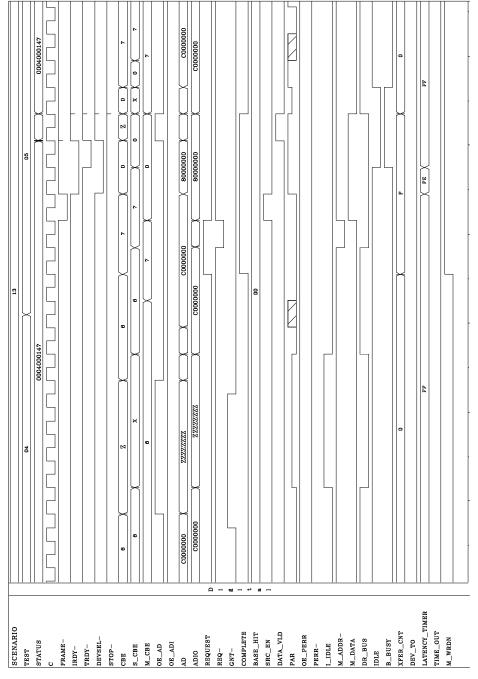

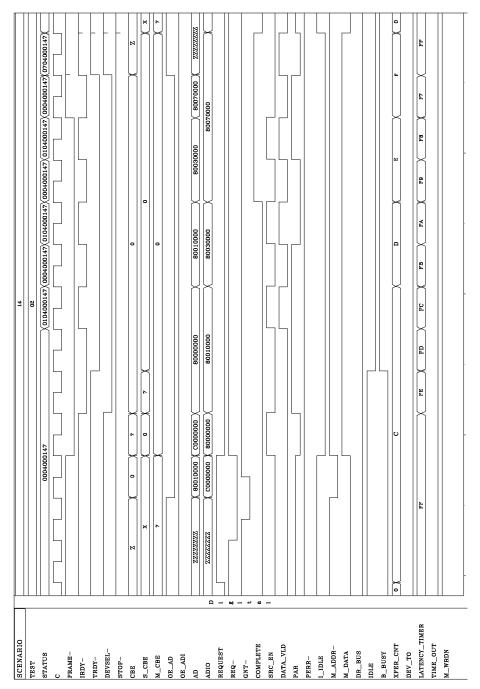

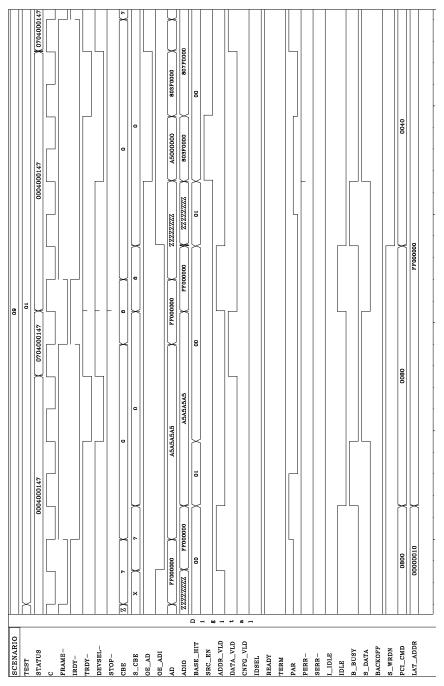

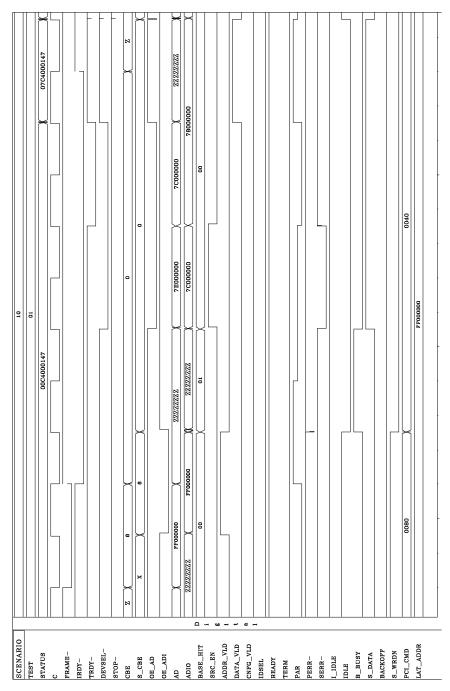

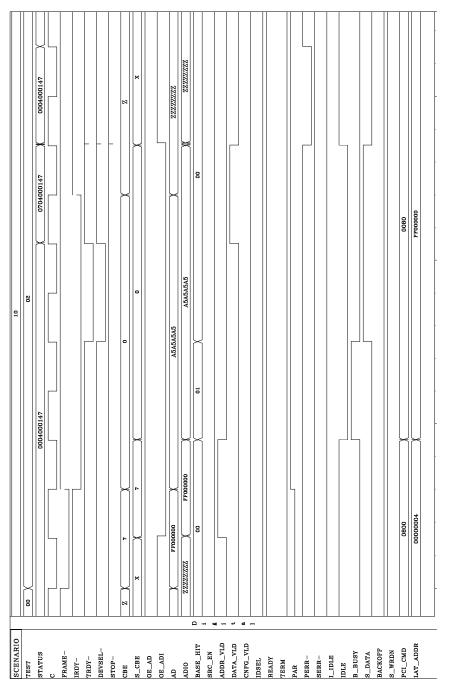

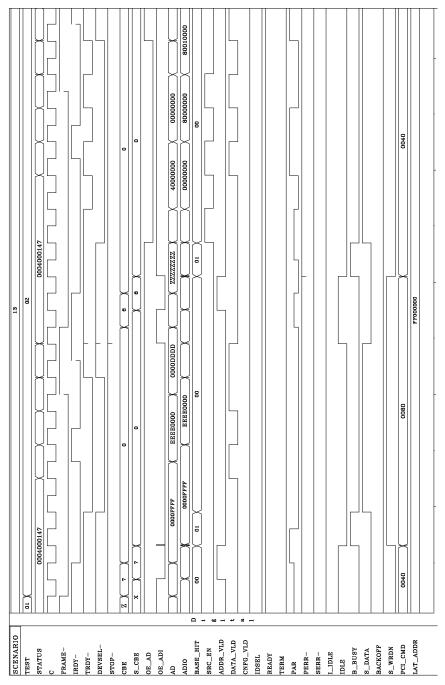

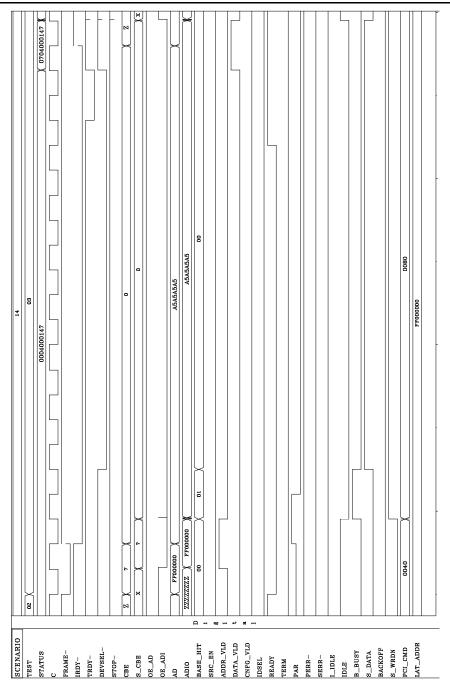

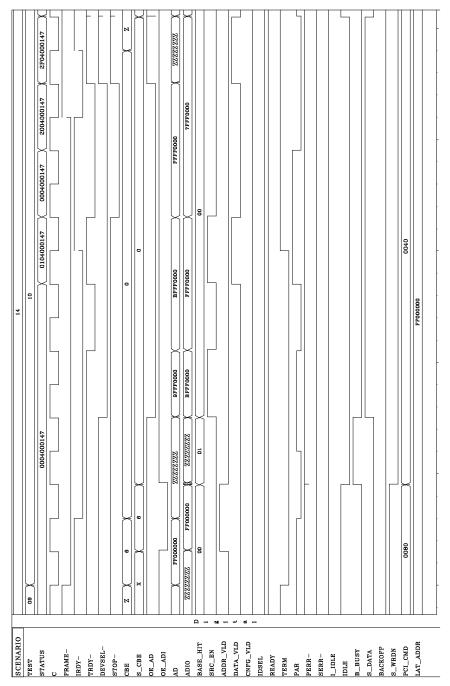

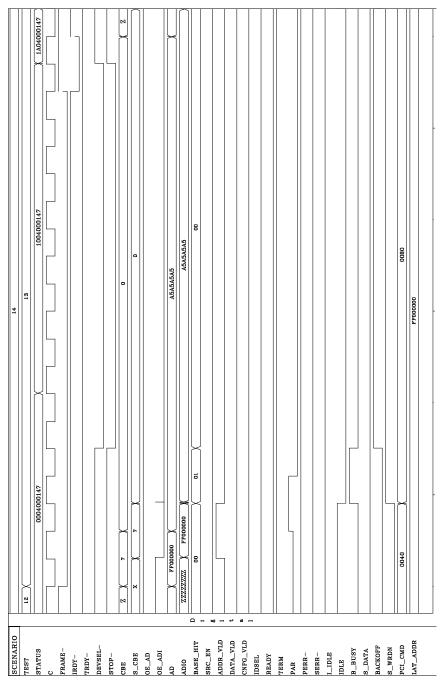

| 21. Appendix C: Waveforms49                      |

| LogiCore Facts<br>LC-DI-PCIM-C, LC-DI-PC | IS-C                          |

|------------------------------------------|-------------------------------|

| Recommended Experier                     | nce Level                     |

| FPGA Design <sup>1</sup>                 | Moderate to Advanced          |

| PCI Protocol and Design                  | Moderate to Advanced          |

| Resources Required                       |                               |

| Packed CLBs                              | 152                           |

| Occupied CLBs                            | 268                           |

| IOBs                                     | 53+                           |

| Performance                              |                               |

| System clock f <sub>max</sub>            | 0-33 MHz                      |

| Supported Devices                        | % Utilized <sup>2</sup>       |

| Master: XC4013E-1PQ2                     | 208C 26%/47%                  |

| Slave: XC4013E-2PQ20                     | 08C                           |

| Design files                             |                               |

| Schematics                               | VIEW <i>logic</i>             |

| Netlist                                  | XNF                           |

| VHDL                                     | Instantiate XNF netlist       |

| Verilog                                  | Instantiate XNF netlist       |

| Verification                             |                               |

| VHDL model                               | Generated by user             |

| Verilog                                  | Generated by user             |

| Testbench                                | VIEWsim Command Files         |

| Required Core Tools                      | XACTstep 5.2.1/6.0.1 or later |

| OURDORT VILLAY WILL DO                   | OVER TECHNICAL CURRENT FOR    |

SUPPORT: XILINX WILL PROVIDE TECHNICAL SUPPORT FOR THIS LOGICORE™ PCI PRODUCT WHEN USED AS DESCRIBED IN THIS USER'S GUIDE OR SUPPORTING APPLICATION NOTES. XILINX CANNOT GUARANTEE TIMING, FUNCTIONALITY, OR SUPPORT OF THIS LOGICORE™ PCI PRODUCT IF IMPLEMENTED IN DEVICES NOT LISTED ABOVE, OR CUSTOMIZED BEYOND THAT REFERENCED IN THIS USER'S GUIDE, OR IF ANY CHANGES ARE DONE IN SECTIONS OF THE DESIGN MARKED AS "DO NOT MODIFY".

Note

Experience building high-performance, pipelined FPGA designs using Xilinx software, Floorplanner, TIMESPECs and guide files recommended.

Packed CLBs/Occupied CLBs

© 1996 Xilinx, Inc. PN: 0401561-01

#### 1. Introduction

This design guide describes how to use the Xilinx LC-DI-PCIM-C LogiCore PCI Master interface and the Xilinx LC-DI-PCIS-C LogiCore PCI Slave interface products. Each Xilinx LogiCore PCI Interface is a fully-integrated, tested, and validated schematic-based PCI Local Bus interface design. The module enables faster implementation of production and prototype FPGA-based PCI applications. The LogiCore PCI Interface is:

- Verified for PCI local bus, revision 2.1, protocol and timing compliance.

- Optimized and pre-placed module for XC4013E FPGA.

- A general-purpose design that can be customized for specific interface requirements by the user and integrated with additional logic.

- Pre-implemented for faster time-to-volume and reduced engineering risk.

The LogiCore PCI Interface provides a high-quality foundation design. The module minimizes the engineering effort required to develop a PCI host interface—saving months of development time. This reduces risk and allows more time to focus on important system-level aspects of the design.

#### 1.1 Overview

The LogiCore PCI Interface is a PCI interface building block created for an XC4013E FPGA device. The detailed schematics form the core PCI interface design. Further customization by the user tailors the design for specific board-level design requirements. Combining a custom user-interface with a fully-tested PCI interface produces a single-chip PCI I/O adapter.

The LogiCore PCI Interface is optimized for both the XC4000E FPGA architecture and for the XACT*step* version 6.0.1/5.2.1 software design flow. Placement constraints, XACT-Performance timing constraints, and a placement guide file guarantee PCI timing requirements.

### 1.2 PCI 2.1 Compliance

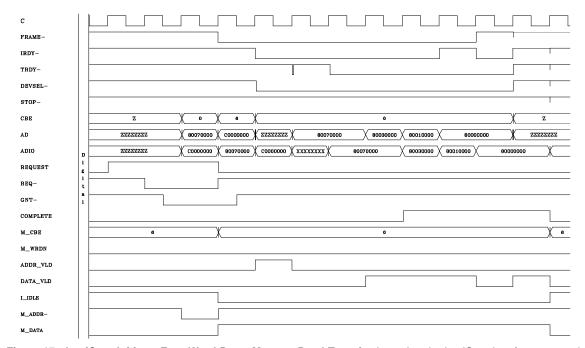

The LogiCore PCI Interfaces have been extensively verified using the VirtualChips VHDL PCI bus simulation model and a Xilinx-created VIEWsim PCI protocol testbench. Both models verify the PCI interface functions according to the test scenarios specified in the *PCI Protocol Compliance Checklist* published by the PCI Special Interest Group (PCI-SIG). The PCI test suite consists of 27 test scenarios, each designed to test compliance of a specific PCI bus protocol. Refer to *LogiCore PCI Interface Protocol Checklist* for a complete list of Xilinx test scenarios, which includes some tests beyond those specified in the PCI-SIG's checklist.

## IMPORTANT!

Due to the complexity of the PCI interface, Xilinx can only guarantee PCI compliance of the LogiCore PCI Interface, as provided, and cannot provide any guarantees for user designs.

#### 1.3 LogiCore PCI Interface Features

- Complete 32-bit PCI Interface

- PCI Local Bus Compliant Revision 2.1

- Target-Only (Slave) or Target/Initiator (Master) PCI support

- 100% programmable single-chip solution

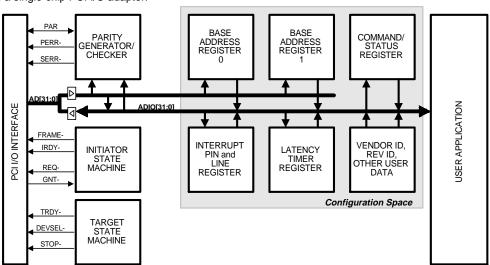

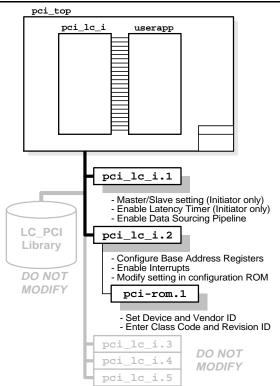

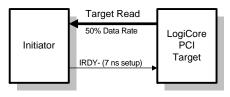

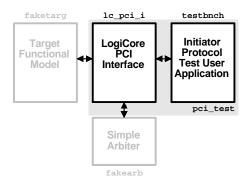

Figure 1. LogiCore PCI Interface block diagram.

## **1.3.1** Initiator Functions (available in LC-DI-PCIM-C only)

- Initiate Memory Read, Memory Write, Memory Read Multiple (MRM), and Memory Read Line (MRL) commands

- Initiate I/O Read and I/O Write commands

- Initiate Configuration Read and Configuration Write commands

- Bus Parking

## **1.3.2 Target Functions** (available in both LC-DI-PCIM-C and LC-DI-PCIS-C products)

- Type 0 Configuration Space Header

- Up to 2 Base Address Registers (memory or I/O with adjustable block sizes from 16 bytes to 256 Mbytes, slow decode speed)

- Parity Generation (PAR) and Parity Error Detection (PERR# and SERR#)

- Memory Read, Memory Write, Memory Read Multiple (MRM), Memory Read Line (MRL), and Memory Write and Invalidate (MWI) command support

- I/O Read and I/O Write command support

- Configuration Read and Configuration Write command support

- 32-bit data transfers, burst transfers with linear address ordering

- Target Abort support

- Target Retry and Target Disconnect support

- Full Command/Status Register support

#### 1.4 Functional Blocks

The LogiCore PCI Interface is partitioned into five major blocks, plus the user application, as shown in Figure 1. These functional blocks include:

- 1. PCI I/O Interface

- 2. Parity Generator/Checker

- Target State Machine

- 4. Initiator State Machine

- Configuration Space

#### 1.4.1 PCI I/O Interface Block

The I/O interface block handles the physical connection to the PCI bus including all signaling, input and output synchronization, output three-state controls, and all request/grant handshaking for bus mastering.

#### 1.4.2 Parity Generator/Checker

Generates/checks even parity across the AD bus, the CBE lines, and the PAR signal. Reports data parity errors via PERR- and address parity errors via SERR-.

#### 1.4.3 Target State Machine

This block manages control over the PCI interface for Target operations. The states implemented are a subset of equations defined in "Appendix B" of the *PCI Local Bus Specification*. The controller is a high-performance state machine using state-per-bit encoding. State-per-bit encoding has narrower and shallower next-state logic functions that more closely match the Xilinx FPGA architecture.

#### 1.4.4 Initiator State Machine (LC-DI-PCIM only)

This block manages control over the PCI interface for Initiator operations. The states implemented are a subset of equations defined in "Appendix B" of the *PCI Local Bus Specification*. The Initiator Control Logic also uses state-per-bit encoding for maximum performance.

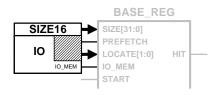

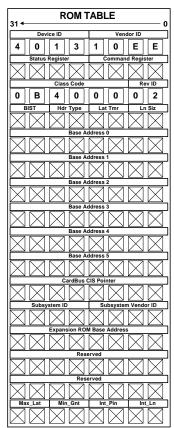

#### 1.4.5 PCI Configuration Space

This block provides the first 64 bytes of Type 0, version 2.1, Configuration Space Header (CSH) to support software-driven "Plug-and Play" initialization and configuration. This includes Command, Status, Latency Timer, Interrupt Pin, Interrupt Line, and two Base Address Registers (BARs), as shown in Figure 1. These BARs illustrate how to implement memory- or I/O-mapped address spaces. Each BAR sets the base address for the interface and allows the system software to determine the addressable range required by the interface. Using a combination of Configurable Logic Block (CLB) flip-flops for the read/write registers and CLB look-up tables for the read-only registers results in optimized packing density and layout.

#### 1.4.6 User Application and Burst FIFOs

The LogiCore PCI Interface provides a simple, generalpurpose interface with a 32-bit data path and latched address for de-multiplexing the PCI address/data bus. The general-purpose user interface allows the rest of the device to be used in a wide range of custom interface applications requiring programmable logic.

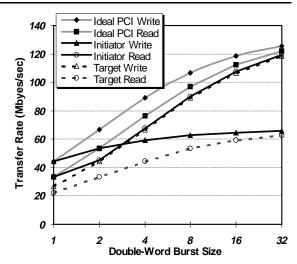

Typically, the user application contains burst FIFOs to increase PCI system performance. PCI derives its performance from its ability to support burst transfers. The performance of any PCI application depends largely on the burst transfer capability of the interface device. Integrated read/write FIFOs, built from the on-chip synchronous RAM available in XC4000E devices, support data transfers in excess of 33 MHz.

#### 2. Getting Started

This document and the LogiCore PCI macro assume that the reader has

- A thorough understanding of the PCI Local Bus

- Previous Xilinx FPGA design experience, specifically with the larger members of the XC4000 FPGA family. Prior experience with XACT-Performance<sup>™</sup> and the Floorplanner software is beneficial.

- Experience building high-performance, heavilypipelined designs.

Xilinx <u>strongly</u> recommends that those unfamiliar with PCI obtain a copy of the **PCI Local Bus Specification** and read the reference book called **PCI System Architecture**, included with the product, before using this Logi-Core design. PCI is a fairly demanding, high-performance application. Users that have never done a Xilinx design before should allow sufficient time to learn the Xilinx design environment.

To start a design using the LogiCore PCI Interface, you will need:

- *PCI Local Bus Specification*, Revision 2.1, dated June 1, 1995 or later.

- VIEWlogic schematic entry and simulation software.

- VIEWlogic libraries for the Xilinx XC4000E FPGA family.

- Xilinx XACTstep version 6.0.1/5.2.1 or later software supporting the XC4000E FPGA family.

- Optional Perl (version 5.0) software (available via the World-Wide Web, see section 20.6) to run selected utilities.

- Optional Adobe Acrobat software to view on-line documentation available on the CD-ROM. Adobe Acrobat is included with the Xilinx XACT step software.

- A workstation or a 100-MHz or faster Pentium<sup>TM</sup> PC with at least 32 Mbytes of RAM and 10 Mbytes of available disk space to hold the design and verification files.

## 3. Design Methodology

The LogiCore PCI Interfaces are highly optimized with floorplanned layout for the XC4013E FPGA device. Relative placement constraints (RLOCs) provide easy implementation of the PCI interface. Pre-placed and prerouted guide files guarantee timing performance on critical control signals like IRDY-, TRDY-, and FRAME-.

As in ASIC devices, FPGAs benefit from floorplanning, especially for designs like the LogiCore PCI Interfaces. These placement attributes help the Partition, Place and Route (PPR) tools to quickly achieve optimal routing results

The user connects the LogiCore PCI Interface to other modules to complete the design. For example, to complete a PCI adapter card interface using the XC4013E, a designer could create a single-page schematic with the Initiator/Target LogiCore PCI Interface component together with the required user application. Next, the user compiles the design using the XACTstep software and the PCI place and route constraints file for the Xilinx XC4013E-2PQ208C. At this point the design can be simulated or downloaded to the target device.

The entire schematic describes a generic PCI interface. If possible, the logic contained in the schematic is trimmed during the design compilation process. The design can be used as is or tuned to meet a specific requirement, according to the guidelines described in this user's guide.

#### 3.1 Modular Construction

The LogiCore PCI Interface, as provided, only supports the XC4013E-2PQ208C FPGA device. The Target-Only and Target/Initiator options require a fixed amount of CLB resources for the core PCI interface. Table 1 shows the percentage of free programmable logic space available after integrating the LogiCore PCI Interface. Note that the Target-Only (Target) design has more free space than does the Target/Initiator (Initiator) design. This is because the Initiator control logic consumes extra resources beyond those used in Target-Only designs.

Table 1. Estimated XC4013E CLB Utilization Chart for LogiCore PCI Interface Plus 16 x 32 FIFO

| Logicore i of interface i las to x 32 i ii o |         |              |        |         |           |  |

|----------------------------------------------|---------|--------------|--------|---------|-----------|--|

|                                              |         | Logic % Free |        | ee CLBs |           |  |

| Device                                       | Package | I/O          | Blocks | Target  | Initiator |  |

| XC4013E                                      | PQ208   | 160          | 576    | 60%     | 50%       |  |

|                                              | PQ240   | 192          |        |         |           |  |

Only the XC4013E device is supported, as delivered. Table 2 presents possible alternative, unsupported solutions. None of these options has been verified through compliance testing.

Table 2. Estimated XC4000E CLB Utilization Chart for Unsupported Alternative Solutions (LogiCore PCI Interface Plus 16 x 32 FIFO)

| (Logicole i di interiace i las lo x cz i ii d) |         |     |        |        |            |  |

|------------------------------------------------|---------|-----|--------|--------|------------|--|

|                                                |         |     | Logic  | % Fre  | e CLBs     |  |

| Device                                         | Package | I/O | Blocks | Target | Initiator* |  |

|                                                |         |     |        | *      |            |  |

| XC4008E                                        | TQ144   | 120 | 324    | 40%    | 30%        |  |

|                                                | PQ160   | 129 |        |        |            |  |

|                                                | PQ208   | 144 |        |        |            |  |

| XC4010E                                        | PQ160   | 129 | 400    | 55%    | 45%        |  |

|                                                | PQ208   | 160 |        |        |            |  |

| XC4020E                                        | PQ208   | 160 | 784    | 70%    | 65%        |  |

|                                                | PQ240   | 193 |        |        |            |  |

<sup>\*</sup> Preliminary estimates

#### 3.2 Selecting the Right Speed Grade

Fully-compliant 33 MHz PCI applications require the XC4000E speed grade shown in Table 3. The XC4013E-1 is recommended for all Master 33 MHz designs, al-

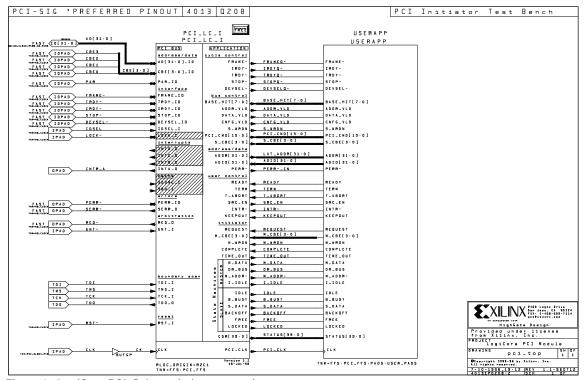

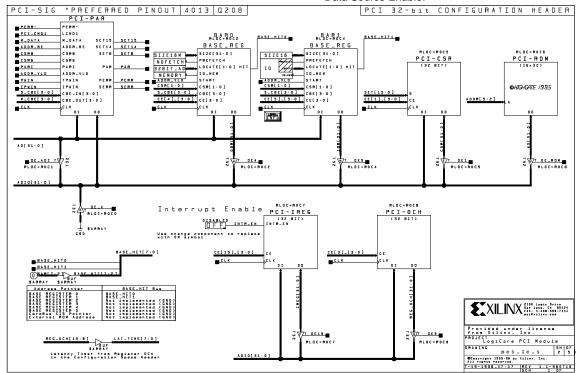

Figure 2. LogiCore PCI Schematic (pci\_top.1).

though Target applications will be able to use the XC4013E-2 speed grade.

Table 3. Speed Grade Required for PCI Applications

| Bus Speed | Slave | Master |

|-----------|-------|--------|

| 25 MHz    | -2    | -2     |

| 33 MHz    |       | -1     |

## 4. LogiCore PCI Interface Operation

The LogiCore PCI Interfaces are designed to interface between the PCI bus and the application interface. An example design with a PCI interface and a user application is shown in the top-level schematic block diagram (pci\_top.1), shown in Figure 2. This example consists of the LogiCore PCI Interface (pci\_lc\_i.1). The user interface provides a complete custom interface to the user application, userapp.1. The PCI interface module, however, needs only minimal customization. The major address/data bus and a small number of control signals connect the PCI interface to the user application.

#### 4.1 LogiCore PCI Interface (PCI\_LC\_I)

This section provides an operational description of the LogiCore PCI Interface (PCI\_LC\_I). The important features of the PCI-to-User-Interface and User-Interface-to-PCI transactions are presented in this section.

The PCI LogiCore Interface supports all the basic PCI functions including:

- Type 0 configuration space support

- I/O read/write functions

- Memory read/write functions

A summary of these basic features as well as enhancements are outlined below.

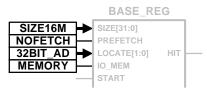

The Target design incorporates two base address registers:

- Base Register 0 (BAR0) configured for memory space with an 8-bit decode (16 Mbyte block)

- Base Register 1 (BAR1) as I/O space with a 28-bit decode (16 byte block)

These registers may be modified by the user to decode from 4 to 28 bits of address space, mapped into either memory or I/O space.

The PCI bus commands are decoded, latched, and available on the PCI\_CMD[15:0] bus from the LogiCore PCI Interface. The commands supported in the design are shown in Table 4.

Full parity support for all read/write functions is largely transparent to the designer. Other embedded PCI control

functions include command decoding, latching functions, output enables, and specific PCI state-machine functions.

#### 4.2 Supported PCI Commands

PCI bus commands direct the Target according to the type of access that the Initiator is requesting. PCI bus commands are encoded on the CBE[3:0] lines during the address phase. Table 4 illustrates the PCI bus commands currently supported by the LogiCore PCI Interface.

The LogiCore Target interface can receive and process a Memory Write and Invalidate. However, the LogiCore Initiator interface does not support the Memory Write and Invalidate command because it does not track the cache line size.

Table 4. PCI Bus Commands

| CBE   |                         | PCI    | PCI    |

|-------|-------------------------|--------|--------|

| [3:0] | Command                 | Master | Slave  |

| 0000  | Interrupt Acknowledge   | No*    | Ignore |

| 0001  | Special Cycle           | No*    | Ignore |

| 0010  | I/O Read                | Yes    | Yes    |

| 0011  | I/O Write               | Yes    | Yes    |

| 0100  | Reserved                | Ignore | Ignore |

| 0101  | Reserved                | Ignore | Ignore |

| 0110  | Memory Read             | Yes    | Yes    |

| 0111  | Memory Write            | Yes    | Yes    |

| 1000  | Reserved                | Ignore | Ignore |

| 1001  | Reserved                | Ignore | Ignore |

| 1010  | Configuration Read      | Yes    | Yes    |

| 1011  | Configuration Write     | Yes    | Yes    |

| 1100  | Memory Read Multiple    | Yes    | Yes    |

| 1101  | Dual Address Cycle      | No*    | Ignore |

| 1110  | Memory Read Line        | Yes    | Yes    |

| 1111  | Memory Write Invalidate | No*    | Yes    |

<sup>\*</sup> The Initiator can present these commands. However, they either require additional user-application logic to support them or have not been thoroughly tested.

### 5. Signal Descriptions

The top-level schematic block diagram (pci\_top.1), shown in Figure 2, is a sample of a PCI function and user application.

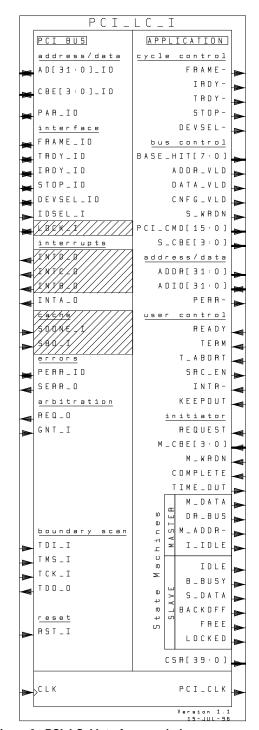

The interface signals are grouped into functional sections with the required PCI bus interface signals on the left-hand side of the interface symbol and all user interface signals on the right-hand side of the symbol.

#### 5.1 PCI Bus Interface Signals

Table 5 defines the interface signals that comprise the PCI Local Bus Interface. Most of the signals are common to both the PCI Target and PCI Initiator/Target modules. Pin locations are device and package dependent. See the appropriate constraint file (\*.cst) for specific device configurations.

#### 5.2 User Interface Signals

The user interface to the LogiCore PCI Interface provides most of the module's internal data paths and state machine control signals. This provides ultimate flexibility for customized user applications.

Table 6 describes the interface signals available on the user interface. Most of the signals are common to both the PCI Target and PCI Initiator/Target modules.

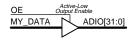

Figure 3. PCI\_LC\_I interface symbol.

Table 5. PCI Bus Interface Signals

|                           |        |           | Table 5. PCI Bus Interface Signals                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                               |  |  |

|---------------------------|--------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Signal Name               | Target | Initiator | Functional Description                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                               |  |  |

| Address/Data Address/Data |        |           |                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                               |  |  |

| AD[31:0]_IO               | I/O    | I/O       | <b>PCI Address/Data Bus</b> - time-multiplexed address/data bus. Each bus transaction consists of an address phase followed by one or more data phases.                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                               |  |  |

|                           |        |           | The ADDR_VLD signal follows the address phase on the PCI bus indicating that the address is now available on the ADIO[31:0] internal bus. During an Initiator transaction, the back-end application should provide address on the ADIO[31:0] internal bus when M_ADDR- is asserted Low.                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                               |  |  |

|                           |        |           | The data phase is indicated by s_DATA during a Target access or by M_DATA during an Initiator operation.                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                               |  |  |

| CBE[3:0]_IO               | In     | I/O       | <b>PCI Command/Byte Enable</b> - time-multiplexed bus command and byte enables. Bus commands (shown in Table 4) are asserted during an address phase on the bus. Byte enables are asserted during data phases.                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                               |  |  |

|                           |        |           | During a Target access to the LogiCore interface, the CBE[3:0]_IO lines drive the s_CBE[3:0] lines to the user application. The command presented on CBE[3:0]_IO is decoded, latched during the address cycle and presented on PCI_CMD[15:0]. Byte enables are presented during the Target data phases (s_DATA).                                                                                           |                                                                                                                                                                                                                                                                                                                                                               |  |  |

|                           |        |           | When operating as an Initiator, the user application drives the CBE[3:0] lines using the M_CBE[3:0] lines on the LogiCore interface. Any command can be presented, but the user application must be able to support any command that it issues. A list of supported commands is shown in Table 4. The user interface must provide valid byte enables during the Initiator data phases (M_DATA).            |                                                                                                                                                                                                                                                                                                                                                               |  |  |

| PAR_IO                    | I/O    | I/O       | PCI Parity signal - generates/checks even parity across AD[31:0]_IO and CBE[3:0]_IO.                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                               |  |  |

|                           |        |           |                                                                                                                                                                                                                                                                                                                                                                                                            | When the LogiCore macro is the source of the data (Target Read, Initiator Write, or Initiator address phase), the macro generates even parity across AD[31:0]_IO and CBE[3:0]_IO and presents the result on PAR_IO one cycle after the values were presented on AD[31:0]_IO and CBE[3:0]_IO. The LogiCore macro always supplies PAR_IO when it provides data. |  |  |

|                           |        |           | When the LogiCore macro receives data (Target Write, Initiator Read, address phase presented by another agent), the macro checks for even parity across the AD[31:0]_IO and CBE[3:0]_IO presented one cycle earlier and the current PAR_IO input. Parity errors are reported via PERR_IO two cycles after data is presented and also reported by Detected Parity Error bit in the Status Register (CSR31). |                                                                                                                                                                                                                                                                                                                                                               |  |  |

| Signal Name | Target | Initiator  | Functional Description                                                                                                                                                                                                                                                                                                   |

|-------------|--------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signal Name | rarget | IIIIIIatoi | Interface                                                                                                                                                                                                                                                                                                                |

| FRAME_IO    | In     | I/O        | Frame - driven by the bus master to indicate a bus transaction. FRAME_IO is asserted Low for the duration of the operation and is de-asserted during the last data cycle to identify the end of the transaction.                                                                                                         |

|             |        |            | When operating as an Initiator, the LogiCore interface will only assert FRAME_IO after                                                                                                                                                                                                                                   |

|             |        |            | ■ receiving GNT_I and                                                                                                                                                                                                                                                                                                    |

|             |        |            | ■ the bus is idle (IRDY_IO and FRAME_IO de-asserted) and                                                                                                                                                                                                                                                                 |

|             |        |            | ■ the Bus Master Enable bit (CSR2) is set in the Command Register and                                                                                                                                                                                                                                                    |

|             |        |            | <ul> <li>the user application has a REQUEST pending (though the REQ_O pin need not<br/>be asserted).</li> </ul>                                                                                                                                                                                                          |

|             |        |            | When operating as an Initiator, the LogiCore interface will de-assert FRAME_IO after                                                                                                                                                                                                                                     |

|             |        |            | ■ the user application asserts COMPLETE, or                                                                                                                                                                                                                                                                              |

|             |        |            | <ul> <li>receiving a termination from the addressed Target (Target Retry, Target<br/>Disconnect, or Target Abort), or</li> </ul>                                                                                                                                                                                         |

|             |        |            | <ul><li>not receiving a DEVSEL- from the addressed Target (Master Abort), or</li></ul>                                                                                                                                                                                                                                   |

|             |        |            | <ul> <li>the Initiator's Latency Timer has expired, if enabled, and the system arbiter is<br/>no longer asserting GNT_I.</li> </ul>                                                                                                                                                                                      |

| TRDY_IO     | Out    | I/O        | <b>Target Ready</b> - indicates that the target module is ready to complete the current data phase. When TRDY_IO is asserted Low, the Target is ready to transfer data.                                                                                                                                                  |

|             |        |            | During a Target Read operation, the LogiCore macro automatically inserts one TRDY- wait-state after each successful data transfer, except the last (see section 13.1). This allows time for the macro to provide new data between transfers.                                                                             |

|             |        |            | During a Target transaction, TRDY- is controlled by the READY signal from the user application and the LogiCore Target state machine.                                                                                                                                                                                    |

| IRDY_IO     | In     | I/O        | Initiator Ready - indicates that the Initiator of the access is able to complete the current data phase. When IRDY_IO is asserted Low, the Initiator is ready to transfer data.                                                                                                                                          |

|             |        |            | During an Initiator Write operation, the LogiCore macro automatically inserts one IRDY- wait-state after each successful data transfer, except the last (see section 13.1). This allows time for the macro to provide new pipelined data between transfers.                                                              |

|             |        |            | The macro also automatically inserts one IRDY- wait-state during an Initiator burst transfer, before de-asserting FRAME_IO after the user application asserted COMPLETE and the current data transfer completes (see section 13.2). This extra wait state is not inserted on single transfers.                           |

|             |        |            | During an Initiator transaction, IRDY- is controlled by the READY signal from the user application and the LogiCore Initiator state machine.                                                                                                                                                                             |

| STOP_IO     | Out    | I/O        | <b>Stop</b> - indicates that the Target has requested to stop the current access. The Target uses STOP_IO to signal a Disconnect (terminate with or without data transfer after the first transfer), Retry (terminate with no data transfer on the first transfer), or Target Abort (serious problem, no data transfer). |

|             |        |            | The <b>TERM</b> signal from the user application directly controls the STOP_IO signal. When <b>TERM</b> is asserted, STOP_IO will be asserted on the next clock edge if the macro is involved in a Target access.                                                                                                        |

| Signal Name | Target | Initiator | Functional Description                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------|--------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DEVSEL_IO   | Out    | I/O       | Device Select - indicates that the Target has decoded the address presented during the address phase and it matches one of the Target's Base Address Registers (BARs). Address decoding is distributed within the PCI system. Each Target monitors each address cycle to determine if it is the agent addressed in the current transaction.                                                                               |

|             |        |           | The LogiCore PCI Target responds with a slow decode speed. If the presented address matches one of the macro's Base Address Registers, then the LogiCore asserts DEVSEL_IO Low on the third clock cycle after the first clock cycle where FRAME_IO is asserted Low.                                                                                                                                                       |

| IDSEL_I     | In     | ln        | Initialization Device Select - indicates the LogiCore macro is the target of a configuration operation. IDSEL_I is asserted High while AD[1:0]_IO='00' indicating a Configuration access.                                                                                                                                                                                                                                 |

|             |        |           | IDSEL_I is usually resistively coupled to one of the higher-order address lines. The specific address line will depend on the card slot's order in the system configuration chain.                                                                                                                                                                                                                                        |

| LOCK_I      | In     | I/O       | Lock - indicates the Initiator has gained exclusive access to a target. Not Supported                                                                                                                                                                                                                                                                                                                                     |

|             |        |           | Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                |

| INTD_O      | OD     | OD        | Interrupt D - indicates the LogiCore PCI Interface requests an interrupt. Not Supported.                                                                                                                                                                                                                                                                                                                                  |

| INTC_O      | OD     | OD        | Interrupt C - indicates the LogiCore PCI Interface requests an interrupt. Not Supported.                                                                                                                                                                                                                                                                                                                                  |

| INTB_O      | OD     | OD        | Interrupt B - indicates the LogiCore PCI Interface requests an interrupt. Not Supported.                                                                                                                                                                                                                                                                                                                                  |

| INTA_O      | OD     | OD        | Interrupt A - indicates the LogiCore PCI Interface requests an interrupt. INTA_O is an open-drain output and should be driven by a flip-flop. The flip-flop is cleared by the interrupt handling routing.                                                                                                                                                                                                                 |

|             |        |           | Cache (NOT SUPPORTED)                                                                                                                                                                                                                                                                                                                                                                                                     |

| SDONE_I     | N/A    | N/A       | PCI SDONE_I signal. Not Supported.                                                                                                                                                                                                                                                                                                                                                                                        |

| SBO_I       | N/A    | N/A       | PCI SBO_I signal. Not Supported.                                                                                                                                                                                                                                                                                                                                                                                          |

|             |        | 1         | Error Signals                                                                                                                                                                                                                                                                                                                                                                                                             |

| PERR_IO     | Out    | I/O       | Parity Error - indicates the module has detected a parity error as the target of a write data transfer or the initiator of a read data transfer. Checks for even parity over the AD[31:0]_IO, CBE[3:0]_IO, and PAR_IO signals. Parity errors are reported two clock cycles after the data transaction appeared on the AD[31:0]_IO and CBE[3:0]_IO lines.                                                                  |

|             |        |           | Parity error reporting on PERR_IO is enabled by setting the Report Parity Errors bit (CSR6) in the Command Register.                                                                                                                                                                                                                                                                                                      |

|             |        |           | Parity errors, except those during Special Cycles, are always reported in the Status Register (CSR31). Additionally, an Initiator reports that it has detected a parity error during a transaction where it was the bus master. The error is reported via the Data Parity Error Detected bit (CSR24) in the Status Register if the Report Parity Errors bit (CSR6) is set in the Command Register.                        |

| SERR_O      | OD     | OD        | System Error - indicates that a parity error was detected during an address cycle. SERR_O does not report parity errors during a Special Cycle. SERR_O is asserted Low on the third clock after FRAME_IO is first recognized as asserted Low. System errors are reported on the Signaled System Error bit (CSR30) in the Status Register if the SERR- Enable bit (CSR8) is set in the Command Register. Opendrain output. |

|             |        |           | Arbitration                                                                                                                                                                                                                                                                                                                                                                                                               |

| REQ_O       | N/A    | Out       | Request PCI Bus - indicates to the arbiter that the LogiCore PCI Initiator requests access to the bus. The Initiator may only request the bus when it has been enabled by setting the Bus Master Enable flag as bit 2 in the Command Register (CSR2). REQ_O is directly controlled by the REQUEST input from the user application.                                                                                        |

$\mathsf{OD} = \mathsf{Open}\text{-drain output}. \ \mathsf{N/A} = \mathsf{Not Applicable}.$

| Signal Name | Target | Initiator  | Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------|--------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GNT_I       | N/A    | In         | Grant PCI Bus - indicates that the arbiter has granted the bus to the LogiCore PCI Interface. Once GNT_I is asserted and REQUEST is asserted by the user application, the LogiCore macro performs an Initiator transaction under the conditions specified in the FRAME_IO entry.                                                                                                                                                                                                        |

|             |        |            | If GNT_I is asserted and there is <i>not</i> a pending <b>REQUEST</b> or the Bus Master Enable bit is not set, then the macro performs Bus Parking (see <b>DR_BUS</b> entry in Table 6).                                                                                                                                                                                                                                                                                                |

|             | Bour   | ndary Scar | n (uses XC4000E dedicated boundary scan function)                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| TDI_I       | In     | In         | Test Data Input - boundary scan serial data input.                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| TMS_I       | In     | In         | Test Mode Select - boundary scan command input.                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| TCK_I       | In     | In         | Test Clock - boundary scan clock input.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| TDO_O       | Out    | Out        | Test Data Output - boundary scan serial data output.                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| RST_I       | In     | In         | Global Reset - resets all internal flip-flops and forces all outputs to a high-impedance state. Uses the dedicated XC4000E global set/reset and global three-state function. Resets the contents of the Command/Status Register. Disables the Initiator functionality until the system software sets the Master Enable bit in the Command Register. Disables memory or I/O Target accesses until the system software sets the Memory Enable or I/O Enable bits in the Command Register. |

| CLK         | In     | In         | PCI Clock - input from PCI bus that drives the entire LogiCore module, and synchronous user applications. The frequency of CLK ranges from DC to 33 MHz. The CLK input must be driven from a primary global clock buffer (BUFGP). The buffer is not integrated in the macro to allow for easier porting to other Xilinx FPGA technologies.                                                                                                                                              |

N/A = Not Applicable for Target-Only function.

Table 6. Connections to the User Interface

| Table 6. Connections to the User Interface |        |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|--------------------------------------------|--------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Signal Name                                | Target | Initiator | Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|                                            |        |           | Cycle Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

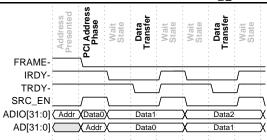

| FRAME-                                     | Out    | Out       | Frame - driven by the bus master to indicate the start and duration of the access. FRAME - is captured in an input flip-flop by the PCI clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|                                            |        |           | The Initiator only asserts FRAME- on the clock cycle following the condition where GNT- and REQ- are asserted and FRAME- and IRDY- are de-asserted on the bus (Bus Idle). Note that the Bus Master Enable bit (CSR2) in Com-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| IRDY-                                      | Out    | Out       | mand Register, must be set before the Initiator can request the bus.  Initiator Ready - driven by the bus master to indicate that it is ready to transfer data. IRDY- is captured in an input flip-flop by the PCI clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| TRDY-                                      | Out    | Out       | Target Ready - driven by the addressed target to indicate that it is ready to transfer data. TRDY- is captured in an input flip-flop by the PCI clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| STOP-                                      | Out    | Out       | Stop Transaction - driven by the addressed target to indicate that it wishes to terminate the current transaction. Data may or may not be transferred when STOP- is asserted, depending on whether TRDY- is asserted. STOP- is captured in an input flip-flop by the PCI clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| DEVSEL-                                    | Out    | Out       | <b>Device Selected</b> - driven by the addressed target to indicate that it is the target of the current transaction. <b>DEVSEL</b> - is captured in an input flip-flop by the PCI clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|                                            |        |           | Bus Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| BASE_HIT[7:0]                              | Out    | Out       | Base Address Hit - indicates that one of the Base Address Registers (BARs)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

|                                            |        |           | is being addressed. The bus is one-hot encoded as indicated below. The BASE_HIT signals are active for one clock cycle, the cycle preceding the s_DATA state (which corresponds to B_BUSY if the address matches). Only BASE_HIT[1:0] are connected in the design as provided. BASE_HIT0 is pre-configured as a memory base register, BASE_HIT1 is pre-configured as an I/O base register. The base registers can be customized for specific applications as described in sections 7.4.2 through 7.4.4. (see Rev. 2.1 PCI Spec., p.187)  BASE_HIT[7:0] Bus 7 6 5 4 3 2 1 0  Expansion ROM Address CardBus CIS Pointer Base Register 3 Base Register 3 Base Register 1 Base Register 1 Base Register 1 Base Register 1 Base Register 0 |  |

| ADDR_VLD                                   | Out    | Out       | Address Valid - indicates the address phase on the PCI bus and that the address is available on the ADIO[31:0] internal bus Latched address information is captured and presented on ADDR[31:0]. The PCI bus command is latched and presented on s_CBE[3:0] and latched, decoded, and presented on PCI_CMD[15:0] during ADDR_VLD. ADDR_VLD is active during both LogiCore Target and Initiator operations but is primarily used by the user application in Target operations. (see Rev. 2.1 PCI Spec., p.246)                                                                                                                                                                                                                         |  |

| DATA_VLD                                   | Out    | Out       | Data Valid - indicates that a data transaction has occurred on the PCI AD[31:0] bus. DATA_VLD is asserted High on the clock cycle after both IRDY- and TRDY- are Low on the PCI bus and either the Target state machine is in the s_DATA state or the Initiator state machine is in the M_DATA state.  When receiving data, DATA_VLD indicates that data is available on the ADIO[31:0] bus lines. When providing data, DATA_VLD indicates that the data was received by the agent on opposite end of the transaction. See section 11.2 for more information.                                                                                                                                                                         |  |

| Signal Name                 | Target                       | Initiator                    | Functional Description                                                                                                                                                                                                                                                                                                                                                                                         |

|-----------------------------|------------------------------|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CNFG_VLD                    | Out                          | Out                          | Configuration Valid - indicates the beginning of a potential configuration cycle. Valid for a single cycle, coincident with ADDR_VID. Does not fully decode a configuration cycle (requires PCI_CMD10 or PCI_CMD11) signals.                                                                                                                                                                                   |

| S_WRDN                      | Out                          | Out                          | Slave Write/Read Direction - indicates a Target Write to the user application when asserted High or a Target Read operation from the user application                                                                                                                                                                                                                                                          |

| (WR_RDIN)                   |                              |                              | when asserted Low. Was called WR_RDIN in Version 1.0.                                                                                                                                                                                                                                                                                                                                                          |

| PCI_CMD[15:0]               | Out                          | Out                          | PCI Bus Command - indicates the current decoded and latched PCI bus operation as defined in Table 4. The PCI_CMD[15:0] bus is a one-hot decoded representation of the CBE[3:0] bus. The command is captured during the address phase on the bus and remains asserted until the next address phase.                                                                                                             |

|                             |                              |                              | PCI_CMD[15:0] Bus                                                                                                                                                                                                                                                                                                                                                                                              |

| S_CBE[3:0]<br>(CBE_IN[3:0]) | Out                          | Out                          | Memory Write & Invalidate  Memory Read Line  Dual Address Cycle  Memory Read  Memory Write  Configuration Write  Configuration Read  Memory Write  I/O Read  Special Cycle Interrupt Acknowledge  Slave Command/Byte Enables - indicates the PCI bus command/byte enables for a Target access to the user application. The PCI bus command appears during the address phase (also see PCI_CMD[15:0]). Byte en- |

|                             |                              |                              | ables are presented during the data phase. Note that byte enables are active                                                                                                                                                                                                                                                                                                                                   |

|                             |                              |                              | low. Was called CBE_IN[3:0] in Version 1.0.                                                                                                                                                                                                                                                                                                                                                                    |

| ADDR[31:0]                  | Out                          | Out                          | Address/Data  Latched Address bus - used for pass-through data cycles and to load user                                                                                                                                                                                                                                                                                                                         |

| 1228( 31.0)                 | Out                          | Out                          | address counters or DMA controllers. Address data is registered on ADDR[31:0] internally by the ADDR_VLD signal and the next rising clock edge.                                                                                                                                                                                                                                                                |

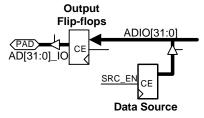

| ADIO[31:0]                  | I/O<br>(internal<br>3-state) | I/O<br>(internal<br>3-state) | Address/Data Bus - the internal bi-directional PCI address/data bus. Used to receive data and to present both address and data information. This bus must be driven using the outputs of internal tri-state buffers (BUFTs).                                                                                                                                                                                   |

|                             | ,                            | ,                            | Note: The user application should never drive the ADIO[31:0] during a                                                                                                                                                                                                                                                                                                                                          |

|                             |                              |                              | Configuration Read operation. The configuration data is stored internal to the LogiCore PCI Interface. The user application should disable output enables during Configuration Read cycles by using the PCI_CMD10 signal.                                                                                                                                                                                      |

| PERR-                       | In                           | In                           | Data Parity Error - indicates <i>any</i> parity errors generated on the PCI bus. PERR- is captured in an input flip-flop by the PCI clock.                                                                                                                                                                                                                                                                     |

| Signal Name | Target                                        | Initiator | Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------|-----------------------------------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <u> </u>    | <u>.                                     </u> |           | User Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |