# Using the Triscend LiteLoader™ Software

January 2002 Version 1.0

## Introduction

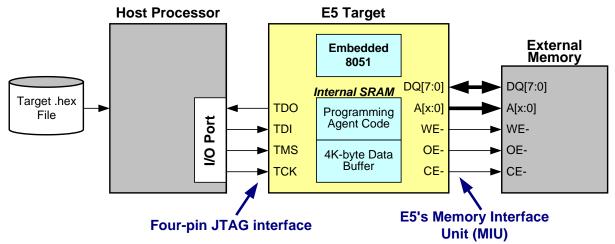

The Triscend LiteLoader™ is a set of ANSI-C software routines that allow a host processor to program a Triscend E5 CSoC device, in system, via a bit-banged JTAG interface. As illustrated in <u>Figure 1</u>, LiteLoader either directly programs an E5 device or downloads a configuration image to an external Flash or serial PROM connected to the E5's Memory Interface Unit (MIU).

Figure 1. LiteLoader either directly programs an E5 device or downloads the E5 initialization data to an external memory connected to the E5's Memory Interface Unit (MIU).

The host processor is some type of intelligent host. It can be another processor or microcontroller in the same system or be an external host like a piece of automated test equipment (ATE) or even a personal computer or handheld computer. In the design example provided, the host processor is another E5 CSoC device.

There is no need to separately compile or modify LiteLoader if using a PC as the intelligent host. Simply use the Triscend FastChip Device Link (FDL) graphical interface or the csoc download command-line function.

The following is a partial list of potential LiteLoader applications.

- A method to configure a stand-alone E5 device that does not have another initialization source.

In these types of applications, there is no Flash or serial PROM connected to the E5's MIU interface. Almost all of the MIU pins would be available to the application as user PIO pins.

- A convenient method to update hardware and software images, either remotely or in the field, without consuming other E5 hardware resources.

- A method to download and execute test functions on an E5 device mounted on the application board via automated test equipment (ATE). The test program running on the E5 device offloads time-consuming or complex tests from the ATE equipment. At the end of the test, the ATE equipment can monitor the status of the test. If the test were successful, the ATE

equipment would then download and program the Flash device connected to the E5 with the latest production release of the hardware and software image.

## **Host Processor Requirements**

The host-side requirements are fairly minimal, as shown below. The communication channel between the host processor and the E5 Target is via a four-line JTAG interface. The LiteLoader code implements a JTAG TAP (Test Access Port) controller in software, via a bit-banged interface.

- Three addressable output port pins (TCK, TMS, TDI)

- One addressable input port pin (TDO)

- The host processor is supported by an ANSI-C compiler

- Ability to access the raw Hex file data to download to the E5 Target device.

In the provided design example, the host E5 device implements a memory-mapped I/O port using Configurable System Logic (CSL) and Programmable Input/Output (PIO) resources. The I/O register is assigned in memory by FastChip using the symbolic address, regJtagTap. The bit definitions for the JTAG interface signals are shown below.

Register Name: regJtagTap

|       | 7 | 6 | 5 | 4 | 3   | 2   | 1   | 0   |

|-------|---|---|---|---|-----|-----|-----|-----|

| Read  | _ | _ | _ | _ | TDO | TDI | TMS | TCK |

| Write | _ | _ | 1 | _ |     | TDI | TMS | TCK |

## Supported Target E5 Download Methods

The LiteLoader program downloads initialization code for the Target E5 to a variety of memory types, as shown below.

- Directly to the Target E5's internal SRAM (download Agent not required)

- External byte-wide Flash memory connected via the Target E5's MIU interface.

- External, in-system programmable serial PROM (Atmel AT17-series) memory connected via the Target E5's MIU interface.

- External byte-wide SRAM memory connected via the Target E5's MIU interface.

## **LiteLoader Download Process**

#### **Access to Target Hex File**

The data for the E5 Target is saved somewhere as an Intel Hex file. It could be stored in Flash memory, stored on a disk, or received via some other communications channel. The specific storage mechanism does not matter. The Hex image is created using the normal FastChip Device Link (FDL) or csoc config configuration flow.

#### **Download Software Agent to Target E5 Device**

The host begins the download process by first downloading a software Agent to the E5 Target device and starts it running. This Agent handles the low-level programming of any external memory. The Agent executes standard 8051 code which is downloaded and executed from the Target E5's internal SRAM memory. The Agent receives data from the host processor in 4K-byte buffer, again

implemented using the Target E5's internal SRAM. Similarly, the host is able to determine the status of the Agent via the JTAG interface.

The host processor then downloads the Flash or Serial PROM (SPROM) algorithm that was previously specified in a data file. The host then sends the Agent a command to erase the external Flash or serial PROM.

#### **Erase External Memory**

The Agent, executing on the Target E5 device, then erases the external memory using the appropriate algorithm, verifies that the external memory was actually erased, and reports status via a register queried by the host processor over JTAG.

## **Download Hex File Data and Program External Memory**

Upon receiving confirmation that the external memory was erased, the host processor downloads the Target Hex image to the Target E5 device. Because the entire Hex image is too big to fit into the Target E5's internal SRAM, the host processor downloads the Hex file in 4K-byte blocks, which are temporarily stored in the Target E5's internal SRAM. After sending a block of data, the host processor issues a command to the Agent to program external memory. This process continues until the entire image is downloaded.

The Agent executing on the Target E5 device then programs the external memory upon receiving each program command from the host. The Agent also verifies that the data was correctly programmed into external memory.

#### Reset Target E5 CSoC Device, Load New Initialization Data

After receiving confirmation that the entire image was downloaded and programmed into external memory, the host processor issues a CSoC Reset command to the Target E5 device via JTAG. The CSoC Reset command is equivalent to asserting the RST- pin on the Target E5 device. On the E5 family, this command is only available via the JTAG interface. The CSoC Reset command forces the Target E5 device to re-initialize itself, booting from external Flash or SPROM. The Target E5 then loads its new configuration data and application code and then begins to execute the new function.

The Target HEX image that is created is then loaded through the Target E5 into FLASH, Serial EEPROM or External RAM (make flash, make SEEPROM, make extsram are the commands used to format the data). The parameters of the memory device to be programmed on the Target E5 board are specified in the respective .DAT files, and can be modified as required.

## **Example Design**

The LiteLoader<sup>™</sup> design example includes a FastChip project, called FCJtagTap, that implements a bit-banged JTAG interface using a Triscend E5 CSoC device as the host processor. As defined in the Makefile, the created JTAG controller is loaded into CSL and then executes the LiteLoader<sup>™</sup> Master Download software from the external RAM on the E5 Development board.

The Target Download Agent is the application code for the Target E5 that is downloaded to the Target E5 by the Master Download software.

## **LiteLoader™ File structure**

# FCJtagTap — FastChip Project Directory

##

Flash.dat

Flash device parameter file

\_seeprom.dat

SEEPROM device parameter file

ExtSram.dat

External SRAM device parameter file

Makefile Cygwin Makefile used to build the download.hex file,

download.cfg file and download to the Master E5 board or

download the demo example to the host E5 board

#### **Demonstration Examples**

Dncounter.ext.hex

Down Counter demo for External SRAM

Dncounter.internal.hex

Down Counter demo for Internal SRAM

Dncounter.seeprom.hex

Down Counter demo for SEEPROM

Upcounter.ext.hex Up Counter demo for External SRAM

Upcounter.seeprom.hexMydesign.seeprom.hexMydesign demo for SEEPROM

## Keil — JtagTap Output Directory

JtagTap

JtagTap.hex Master HEX file

JtagTap.m51

JtagTap.prj

#### Src — LiteLoader™ C Source Directory

JtagTap.h

Te5disp.h

Te5dl.h

Te5flash.h Target Download Agent for Flash

Te5jtag.h

□ Te5sprom.h Target Download Agent for SEEPROM

Te5tap.h

Te5types.h Master data types

Te5utils.h

■ JtagTap.c Master Main

■ Te5disp.c Master 7-segment Display Routines

■ Te5dl.c Master Download Routines

■ Te5jtag.c Master to Target JTAG Routines

■ Te5tap.c Master TAP Software State Machine

| Te5utils.c         | Master Little/Big Endian Conversion Routines                                                                                                                           |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| e5flash.hex        | Target Download Agent FLASH HEX file                                                                                                                                   |

| e5seeprom.hex      | Target Download Agent SEEPROM HEX file                                                                                                                                 |

| HexSplitter.pl     | Perl script used to split a single HEXFILE created by HexToDownload.pl into multiple hex files so that each output file only contains a range of addresses within 64K. |

| HexToDownloader.pl | Perl script used to combine the memory device '.dat' files,<br>Master software and Target HEX image into the<br>download.hex file.                                     |

| HexToStruct.pl     | Perl script to convert Flash and SEEPROM Target Download Agents to header files.                                                                                       |

# LiteLoader™ Instructions

- 1. Use FastChip Device Link (FDL) to create the Target HEX image by selecting the HEX output format.

- 2. Copy the resulting HEX file into the LiteLoader™ HEX directory.

- 3. Configure the appropriate device file for the memory device on the Target E5 board.

- \_Flash.dat Flash device file

- \_Seeprom.dat SEEPROM device file

- \_ExtSram.dat External SRAM device file

- 4. With the appropriate \*.dat file, configure the following variables.

- @IMAGES = ("<Target HEX image>.hex");

- \$MEMORY\_CAP = <Size of device in kilobytes (KB)>;

- \$MEMORY\_ALG = "<Device name from support list>";

- 5. Run Makefile for the appropriate target

- make flash build for FLASH on the Target E5 board

- make seeprom build for SEEPROM on the Target E5 board

- make extsram build for External SRAM on the Target E5 board

- make demo download the demo examples to the Target E5 board

## **Licensing and Restrictions**

#### SOFTWARE DISTRIBUTION AGREEMENT

THE TRISCEND JTAG LITELOADER SOFTWARE PROGRAM AND EXECUTABLE FILES, AND RELATED SPECIFICATION DOCUMENTATION ("PROGRAMS") ARE MADE FREELY AVAILABLE FOR USE BY ANYONE, SUBJECT TO CERTAIN TERMS AND CONDITIONS SET FORTH BELOW. PLEASE READ THESE TERMS AND CONDITIONS CAREFULLY BEFORE DOWNLOADING OR USING THE PROGRAMS. BY DOWNLOADING OR USING THE PROGRAMS, YOU INDICATE YOUR ACCEPTANCE OF THESE TERMS AND CONDITIONS, WHICH CONSTITUTE THE LICENSE AGREEMENT (the "AGREEMENT") BETWEEN YOU AND TRISCEND CORPORATION ("Triscend") WITH REGARD TO THE PROGRAMS. IN THE EVENT THAT YOU DO NOT AGREE WITH ANY OF THESE TERMS AND CONDITIONS, DO NOT DOWNLOAD THE PROGRAMS OR PROMPTLY RETURN THE PROGRAMS TO TRISCEND UNUSED.

#### **License Terms**

Subject to the terms and conditions of this Agreement, Triscend grants to you a worldwide, nonexclusive, perpetual license (with the right to grant sublicenses, and authorize sublicensees to sublicense further) to use, copy, prepare derivative works based on, and distribute the Programs and derivative works thereof, provided that any distribution or sublicense is subject to the same terms and conditions that you use for distribution of your own comparable software products. Any copies of the Programs or derivative works thereof will continue to be subject to the terms and conditions of this Agreement. You must include in any copies of the Programs or derivative works thereof any trademark, copyright, and other proprietary rights notices included in the Programs by Triscend.

#### **Disclaimer of Warranties and Remedies**

NO WARRANTIES, EITHER EXPRESS OR IMPLIED, ARE MADE WITH RESPECT TO THE PROGRAMS, INCLUDING, BUT NOT LIMITED TO, IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, TITLE AND NONINFRINGEMENT, AND TRISCEND EXPRESSLY DISCLAIM ALL WARRANTIES NOT STATED HEREIN. YOU ASSUME THE ENTIRE RISK AS TO THE QUALITY, USE, AND PERFORMANCE OF THE PROGRAMS. SHOULD THE PROGRAMS PROVE DEFECTIVE OR FAIL TO PERFORM PROPERLY, YOU -- AND NOT TRISCEND -- SHALL ASSUME THE ENTIRE COST AND RISK OF ANY REPAIR, SERVICE, CORRECTION, OR ANY OTHER LIABILITY OR DAMAGES CAUSED BY OR OTHERWISE ASSOCIATED WITH THE PROGRAMS. TRISCEND DOES NOT WARRANT THAT THE PROGRAMS WILL MEET YOUR REQUIREMENTS, OR THAT THE OPERATION OF THE PROGRAMS WILL BE UNINTERRUPTED OR ERROR-FREE. YOU ALSO ASSUME RESPONSIBILITY FOR THE SELECTION, INSTALLATION, USE, AND RESULTS OF USING THE PROGRAMS. Some states do not allow the exclusion of implied warranties, so the above exclusion may not apply to you.

TRISCEND SHALL NOT BE LIABLE TO YOU OR ANY OTHER PERSON FOR ANY DAMAGES, INCLUDING ANY INCIDENTAL OR CONSEQUENTIAL DAMAGES, EXPENSES, LOST PROFITS, LOST SAVINGS, OR OTHER DAMAGES ARISING OUT OF OR OTHERWISE ASSOCIATED WITH THE USE OF OR INABILITY TO USE THE PROGRAMS. IN ANY EVENT, TRISCEND'S LIABILITY UNDER THIS AGREEMENT SHALL NOT EXCEED THE LARGER OF EITHER THE AMOUNT YOU PAID TRISCEND FOR USE OF THE PROGRAMS, OR ONE HUNDRED DOLLARS (\$100). YOUR SOLE REMEDIES AND TRISCEND'S ENTIRE LIABILITY ARE AS SET FORTH ABOVE. Some states do not allow the limitation or exclusion of incidental or consequential damages, so the above limitations or exclusions may not apply to you.

To the extent that the Programs are derived from third-party software or other third-party materials, no such third-party provides any warranties with respect to the Programs, assumes any liability regarding use of the Programs, or undertakes to furnish you any support or information relating to the Programs.

#### General

You acknowledge that Triscend is not responsible for and is not obligated to provide, any support, including E-mail and telephone support, for any purpose with respect to the Programs.

You acknowledge that the Programs are made freely available in accordance with this Agreement as part of an effort to promote broad use of the Programs with minimum interference by you and Triscend. Accordingly, you agree that, if you obtain any patents relating to inventions or discoveries made through use of or access to the Programs or derivative works thereof, or that are necessary for the use of the Programs, you will not bring any claim for infringement thereof against Triscend or any direct or indirect licensee of Triscend in connection with or use of the Programs or derivative works thereof. The foregoing does not constitute a license of any copyright or trade secret.

You shall not export the Programs, or any product programmed by the Programs, without first obtaining any necessary U.S. or other governmental licenses and approvals.

This Agreement is entered into for the benefit of Triscend and Triscend's licensors and all rights granted to you and all obligations owed to Triscend shall be enforceable by Triscend and its licensors. This Agreement constitutes the entire understanding and agreement applicable to the Programs, superseding any prior or contemporaneous understandings or agreements. It may not be modified except in a writing executed by Triscend.

This Agreement will be governed by the laws of the State of California. You agree to submit to the jurisdiction of the courts in the State of California for the resolution of any dispute or claim arising out of or relating to this Agreement.

The prevailing party in any legal action or arbitration arising out of this Agreement shall be entitled to reimbursement for its expenses, including court costs and reasonable attorneys' fees, in addition to any other rights and remedies such party may have.

BY USING THE PROGRAMS YOU ACKNOWLEDGE THAT YOU HAVE READ THIS AGREEMENT, UNDERSTAND IT, AND AGREE TO BE BOUND BY ITS TERMS AND CONDITIONS; YOU FURTHER AGREE THAT IT IS THE COMPLETE AND EXCLUSIVE STATEMENT OF THE AGREEMENT BETWEEN YOU AND TRISCEND WHICH SUPERSEDES ANY PROPOSAL OR PRIOR AGREEMENT, ORAL OR WRITTEN, AND ANY OTHER COMMUNICATIONS BETWEEN YOU AND TRISCEND RELATING TO THE SUBJECT MATTER OF THIS AGREEMENT.

#### U.S. Government Restricted Rights

The Programs and any accompanying documentation are provided with RESTRICTED RIGHTS. Use, duplication, or disclosure by the Government is subject to restrictions as set forth in subparagraph (c)(1)(ii) of The Rights in Technical Data and Computer Software clause at DFARS 252.227-7013 or subparagraphs (c)(1) and (2) of Commercial Computer Software--Restricted Rights at 48 CFR 52.227-19, as applicable. Contractor/manufacturer is Triscend Corporation, 301 N. Whisman Rd., Mountain View, California 94043, and its licensors.

#### **Revision History**

| Revision | Date     | Comment         |

|----------|----------|-----------------|

| 1.0      | JAN-2002 | Initial release |

Triscend Corporation

301 North Whisman Road Mountain View, CA 94043-3969 USA Tel: 1-650-968-8668 Fax: 1-650-934-9393 Web: www.triscend.com